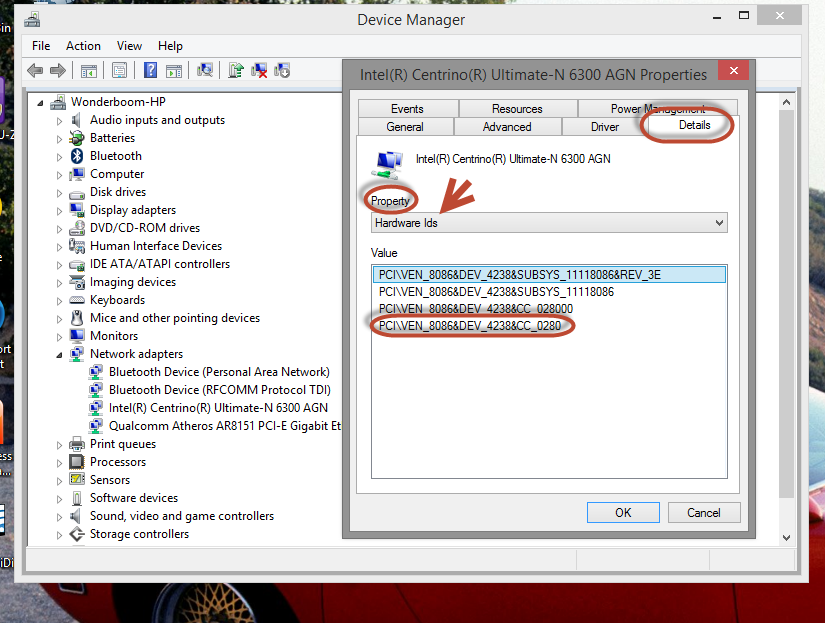

2nd Generation Intel Core Processor Family PCI Express Controller - 0101 Intel 6 series/C206 Series Chipset Family PCI Express Root Port 1 - 1C10 Devices plugged into the computer are a USB mouse, USB keyboard, and LAN. The only other thing plugged in is the monitor, so this is a very basic setup. DOWNLOAD JUST FINE. Pci express root complex windows 10 NO VIRUSES ETHER. 10-Mar-20 05:26 Thank you! Good work 13-Jul-19 05:36 i am using virus protection,Pci express root complex windows 10 norton, no viruses! 01-Apr-19 08:19 Thank you! 19-Nov-18 11:50 Awesome! 02-Jul-18 05:06 nice work 09-Apr-18 18:46 Nice Pci express root.

-->Pci Express Root Complex Driver Lenovo

Overview of the Pci technology.

The Pci technology is not associated with any headers.

Enumerations

Pci Express Root Complex Driver Hp

| Title | Description |

|---|---|

| NPEM_CONTROL_STANDARD_CONTROL_BIT |

Functions

| Title | Description |

|---|---|

| ENABLE_VIRTUALIZATION | The EnableVirtualization routine enables or disables virtualization for a PCI Express (PCIe) device that supports the single root I/O virtualization (SR-IOV) interface. |

| GET_VIRTUAL_DEVICE_DATA | The GetVirtualFunctionData routine reads data from the PCI Express (PCIe) configuration space of a virtual function (VF) on a device that supports the single root I/O virtualization (SR-IOV) interface. |

| GET_VIRTUAL_DEVICE_LOCATION | The GetLocation routine returns the device location of a PCI Express (PCIe) virtual function (VF) on a PCI bus. A device that supports the single root I/O virtualization (SR-IOV) interface can expose one or more VFs on the PCI bus. |

| GET_VIRTUAL_DEVICE_RESOURCES | The GetResources routine returns the resources that the PCI Express (PCIe) physical function (PF) requires in order to enable virtualization on a device that supports the single root I/O virtualization (SR-IOV) interface. |

| GET_VIRTUAL_FUNCTION_PROBED_BARS | The GetVirtualFunctionProbedBars routine returns the values of the PCI Express (PCIe) Base Address Registers (BARs) of a device that supports the single root I/O virtualization (SR-IOV) interface. |

| NPEM_CONTROL_ENABLE_DISABLE | |

| NPEM_CONTROL_QUERY_STANDARD_CAPABILITIES | |

| NPEM_CONTROL_SET_STANDARD_CONTROL | |

| SET_VIRTUAL_DEVICE_DATA | The SetVirtualFunctionData routine writes data to the PCI Express (PCIe) configuration space of a virtual function (VF) on a device that supports the single root I/O virtualization (SR-IOV) interface. |

Structures

What Is Pci Express Root Complex

| Title | Description |

|---|---|

| NPEM_CAPABILITY_STANDARD | |

| NPEM_CONTROL_INTERFACE | |

| PCI_CAPABILITIES_HEADER | The PCI_CAPABILITIES_HEADER structure defines a header that is present in every PCI capability structure. |

| PCI_DEVICE_PRESENT_INTERFACE | The PCI_DEVICE_PRESENT_INTERFACE structure is reserved for system use. |

| PCI_EXPRESS_AER_CAPABILITIES | The PCI_EXPRESS_AER_CAPABILITIES structure describes a PCI Express (PCIe) advanced error capabilities and control register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_AER_CAPABILITY | The PCI_EXPRESS_AER_CAPABILITY structure describes a PCI Express (PCIe) advanced error reporting capability structure. |

| PCI_EXPRESS_BRIDGE_AER_CAPABILITY | The PCI_EXPRESS_BRIDGE_AER_CAPABILITY structure describes a PCI Express (PCIe) advanced error reporting capability structure for a PCIe bridge device. |

| PCI_EXPRESS_CAPABILITIES_REGISTER | The PCI_EXPRESS_CAPABILITIES_REGISTER structure describes a PCI Express (PCIe) capabilities register of a PCIe capability structure. |

| PCI_EXPRESS_CAPABILITY | The PCI_EXPRESS_CAPABILITY structure describes a PCI Express (PCIe) capability structure. |

| PCI_EXPRESS_CORRECTABLE_ERROR_MASK | The PCI_EXPRESS_CORRECTABLE_ERROR_MASK structure describes a PCI Express (PCIe) correctable error mask register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_CORRECTABLE_ERROR_STATUS | The PCI_EXPRESS_CORRECTABLE_ERROR_STATUS structure describes a PCI Express (PCIe) correctable error status register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_DESIGNATED_VENDOR_SPECIFIC_CAPABILITY | Represents the Designated Vendor-Specific Extended Capability defined by PCI-SIG. |

| PCI_EXPRESS_DESIGNATED_VENDOR_SPECIFIC_HEADER_1 | Represents the Designated Vendor-Specific Extended Capability Header 1 defined by PCI-SIG. |

| PCI_EXPRESS_DESIGNATED_VENDOR_SPECIFIC_HEADER_2 | Represents the Designated Vendor-Specific Extended Capability Header 2 defined by PCI-SIG. |

| PCI_EXPRESS_DEVICE_CAPABILITIES_REGISTER | The PCI_EXPRESS_DEVICE_CAPABILITIES_REGISTER structure describes a PCI Express (PCIe) device capabilities register of a PCIe capability structure. |

| PCI_EXPRESS_DEVICE_CONTROL_REGISTER | The PCI_EXPRESS_DEVICE_CONTROL_REGISTER structure describes a PCI Express (PCIe) device control register of a PCIe capability structure. |

| PCI_EXPRESS_DEVICE_STATUS_REGISTER | The PCI_EXPRESS_DEVICE_STATUS_REGISTER structure describes a PCI Express (PCIe) device status register of a PCIe capability structure. |

| PCI_EXPRESS_DPC_CAPABILITY | |

| PCI_EXPRESS_DPC_CAPS_REGISTER | |

| PCI_EXPRESS_DPC_CONTROL_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_EXCEPTION_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_HEADERLOG_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_IMPSPECLOG_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_MASK_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_SEVERITY_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_STATUS_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_SYSERR_REGISTER | |

| PCI_EXPRESS_DPC_RP_PIO_TLPPREFIXLOG_REGISTER | |

| PCI_EXPRESS_DPC_STATUS_REGISTER | |

| PCI_EXPRESS_ENHANCED_CAPABILITY_HEADER | The PCI_EXPRESS_ENHANCED_CAPABILITY_HEADER structure describes the header for a PCI Express (PCIe) extended capability structure. |

| PCI_EXPRESS_ERROR_SOURCE_ID | The PCI_EXPRESS_ERROR_SOURCE_ID structure describes the identifiers of the first correctable error and the first uncorrectable error that are reported in the PCI Express (PCIe) root error status register. |

| PCI_EXPRESS_LANE_ERROR_STATUS | |

| PCI_EXPRESS_LINK_CAPABILITIES_REGISTER | The PCI_EXPRESS_LINK_CAPABILITIES_REGISTER structure describes a PCI Express (PCIe) link capabilities register of a PCIe capability structure. |

| PCI_EXPRESS_LINK_CONTROL_REGISTER | The PCI_EXPRESS_LINK_CONTROL_REGISTER structure describes a PCI Express (PCIe) link control register of a PCIe capability structure. |

| PCI_EXPRESS_LINK_CONTROL3 | |

| PCI_EXPRESS_LINK_QUIESCENT_INTERFACE | The PCI_EXPRESS_LINK_QUIESCENT_INTERFACE structure is reserved for system use. |

| PCI_EXPRESS_LINK_STATUS_REGISTER | The PCI_EXPRESS_LINK_STATUS_REGISTER structure describes a PCI Express (PCIe) link status register of a PCIe capability structure. |

| PCI_EXPRESS_NPEM_CAPABILITY | |

| PCI_EXPRESS_NPEM_CAPABILITY_REGISTER | |

| PCI_EXPRESS_NPEM_CONTROL_REGISTER | |

| PCI_EXPRESS_NPEM_STATUS_REGISTER | |

| PCI_EXPRESS_PME_REQUESTOR_ID | The PCI_EXPRESS_PME_REQUESTOR_ID structure describes the identifier of the requester of a power management event (PME). |

| PCI_EXPRESS_PTM_CAPABILITY | Reserved. Do not use. |

| PCI_EXPRESS_PTM_CAPABILITY_REGISTER | Reserved. Do not use. |

| PCI_EXPRESS_PTM_CONTROL_REGISTER | Reserved. Do not use. |

| PCI_EXPRESS_ROOT_CAPABILITIES_REGISTER | The PCI_EXPRESS_ROOT_CAPABILITIES_REGISTER structure describes a PCI Express (PCIe) root capabilities register of a PCIe capability structure. |

| PCI_EXPRESS_ROOT_CONTROL_REGISTER | The PCI_EXPRESS_ROOT_CONTROL_REGISTER structure describes a PCI Express (PCIe) root control register of a PCIe capability structure. |

| PCI_EXPRESS_ROOT_ERROR_COMMAND | The PCI_EXPRESS_ROOT_ERROR_COMMAND structure describes a PCI Express (PCIe) root error command register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_ROOT_ERROR_STATUS | The PCI_EXPRESS_ROOT_ERROR_STATUS structure describes a PCI Express (PCIe) root error status register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_ROOT_PORT_INTERFACE | The PCI_EXPRESS_ROOT_PORT_INTERFACE structure is reserved for system use. |

| PCI_EXPRESS_ROOT_STATUS_REGISTER | The PCI_EXPRESS_ROOT_STATUS_REGISTER structure describes a PCI Express (PCIe) root status register of a PCIe capability structure. |

| PCI_EXPRESS_ROOTPORT_AER_CAPABILITY | The PCI_EXPRESS_ROOTPORT_AER_CAPABILITY structure describes a PCI Express (PCIe) advanced error reporting capability structure for a root port or a root complex event collector. |

| PCI_EXPRESS_SEC_AER_CAPABILITIES | The PCI_EXPRESS_SEC_AER_CAPABILITIES structure describes a PCI Express (PCIe) secondary error capabilities and control register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_MASK | The PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_MASK structure describes a PCI Express (PCIe) secondary uncorrectable error mask register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_SEVERITY | The PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_SEVERITY structure describes a PCI Express (PCIe) secondary uncorrectable error severity register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_STATUS | The PCI_EXPRESS_SEC_UNCORRECTABLE_ERROR_STATUS structure describes a PCI Express (PCIe) secondary uncorrectable error status register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_SECONDARY_CAPABILITY | |

| PCI_EXPRESS_SERIAL_NUMBER_CAPABILITY | The PCI_EXPRESS_SERIAL_NUMBER_CAPABILITY structure describes a serial number for a PCI Express (PCIe) device. |

| PCI_EXPRESS_SLOT_CAPABILITIES_REGISTER | The PCI_EXPRESS_SLOT_CAPABILITIES_REGISTER structure describes a PCI Express (PCIe) slot capabilities register of a PCIe capability structure. |

| PCI_EXPRESS_SLOT_CONTROL_REGISTER | The PCI_EXPRESS_SLOT_CONTROL_REGISTER structure describes a PCI Express (PCIe) slot control register of a PCIe capability structure. |

| PCI_EXPRESS_SLOT_STATUS_REGISTER | The PCI_EXPRESS_SLOT_STATUS_REGISTER structure describes a PCI Express (PCIe) slot status register of a PCIe capability structure. |

| PCI_EXPRESS_UNCORRECTABLE_ERROR_MASK | The PCI_EXPRESS_UNCORRECTABLE_ERROR_MASK structure describes a PCI Express (PCIe) uncorrectable error mask register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_UNCORRECTABLE_ERROR_SEVERITY | The PCI_EXPRESS_UNCORRECTABLE_ERROR_SEVERITY structure describes a PCI Express (PCIe) uncorrectable error severity register of a PCIe advanced error reporting capability structure. |

| PCI_EXPRESS_UNCORRECTABLE_ERROR_STATUS | The PCI_EXPRESS_UNCORRECTABLE_ERROR_STATUS structure describes a PCI Express (PCIe) uncorrectable error status register of a PCIe advanced error reporting capability structure. |

| PCI_FPB_CAPABILITIES_REGISTER | The Flattening Portal Bridge (FPB) Capabilities register. See section 7.y.2. |

| PCI_FPB_CAPABILITY | Flattening Portal Bridge (FPB) Capabilities that is required for any bridge Function that implements FPB. See section 7.y. |

| PCI_FPB_CAPABILITY_HEADER | The Flattening Portal Bridge (FPB) Capabilities header. See section 7.y.1. |

| PCI_FPB_MEM_HIGH_VECTOR_CONTROL1_REGISTER | The FPB MEM High Vector Control 1 Register. See section 7.y.6. |

| PCI_FPB_MEM_HIGH_VECTOR_CONTROL2_REGISTER | The FPB MEM High Vector Control 2 Register. See section 7.y.7. |

| PCI_FPB_MEM_LOW_VECTOR_CONTROL_REGISTER | FPB MEM Low Vector Control Register. See section 7.y.5. |

| PCI_FPB_RID_VECTOR_CONTROL1_REGISTER | The FPB RID Vector Control 1 Register. See section 7.y.3. |

| PCI_FPB_RID_VECTOR_CONTROL2_REGISTER | The FPB RID Vector Control 1 Register. See section 7.y.3. |

| PCI_FPB_VECTOR_ACCESS_CONTROL_REGISTER | The FPB Vector Access Control Register. See section 7.y.8. |

| PCI_FPB_VECTOR_ACCESS_DATA_REGISTER | The FPB Vector Access Data Register. See section 7.y.9. |

| PCI_PM_CAPABILITY | The PCI_PM_CAPABILITY structure reports the power management capabilities of the device. |

| PCI_PMC | The PCI_PMC structure is used to report the contents of the power management capabilities register. |

| PCI_PMCSR | The PCI_PMCSR structure is used to report the contents of the device's power management control status register. |

| PCI_PMCSR_BSE | The PCI_PMCSR_BSE structure is used to report the contents of the power management control status register for PCI bridge support extensions. |

| PCI_X_CAPABILITY | The PCI_X_CAPABILITY structure reports the contents of the command and status registers of a device that is compliant with the PCI-X Addendum to the PCI Local Bus Specification. |